FLIP-FLOP

Flip-flop adalah keluarga Multivibrator yang mempunyai dua keadaaan stabil atau disebut Bistobil Multivibrator. Rangkaian flip-flop mempunyai sifat sekuensial karena sistem kerjanya diatur dengan jam atau pulsa, yaitu sistem-sistem tersebut bekerja secara sinkron dengan deretan pulsa berperiode T yang disebut jam sistem (System Clock atau disingkat menjadi CK). Seperti yang ditunjukkan dalam gambar 1:

Gambar1: Keluaran dari pembangkit pulsa yang digunakan sebagai deretan pulsa untuk sinkronisasi suatu sistem digital sekuensial Lebor pulsa tp diandaikan kecil terhadap T.

Berbeda dengan uraian materi sebelumnya yang bekerja atas dasar gerbang logika dan logika kombinasi, keluarannya pada saat tertentu hanya tergantung pada harga-harga masukan pada saat yang sama. Sistem seperti ini dinamakan tidak memiliki memori. Disamping itu bahwa sistem tersebut menghafal hubungan fungsional antara variabel keluaran dan variabel masukan. Sedangkan fungsi rangkaian flip-flop yang utama adalah sebagai memori (menyimpan informasi) 1 bit atau suatu sel penyimpan 1 bit. Selain itu flip-flop juga dapat digunakan pada Rangkaian Shift Register, rangkaian Counter dan lain sebagainya.

Macam - macam Flip-Flop:

1. RS Flip-Flop

2. CRS Flip-Flop

3. D Flip-Flop

4. T Flip-Flop

5. J-K Flip-Flop

RS Flip-Flop

RS Flip-Flop yaitu rangkaian Flip-Flop yang mempunyai 2 jalan keluar Q dan Q (atasnya digaris). Simbol-simbol yang ada pada jalan keluar selalu berlawanan satu dengan yang lain. RS-FF adalah flip-flop dasar yang memiliki dua masukan yaitu R (Reset) dan S (Set). Bila S diberi logika 1 dan R diberi logika 0, maka output Q akan berada pada logika 0 dan Q not pada logika 1. Bila R diberi logika 1 dan S diberi logika 0 maka keadaan output akan berubah menjadi Q berada pada logik 1 dan Q not pada logika 0.

Sifat paling penting dari Flip-Flop adalah bahwa sistem ini dapat menempati salah satu dari dua keadaan stabil yaitu stabil I diperoleh saat Q =1 dan Q not = 0, stabil ke II diperoleh saat Q=0 dan Q not = 1 yang diperlihatkan pada gambar berikut:

Gambar 2. RS-FF yang disusun dari gerbang NAND

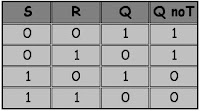

Tabel Kebenaran:

keterangan:

memory = 1/0

dont care = Q dan Qnot nilainya 1 atau 0

Q = 0 [reset]

Q = 1 [set]

Yang dimaksud kondisi terlarang yaitu keadaaan yang tidak diperbolehkan kondisi output Q sama dengan Q not yaitu pada saat S=0 dan R=0. Yang dimaksud dengan kondisi memori yaitu saat S=1 dan R=1, output Q dan Qnot akan menghasilkan perbedaan yaitu jika Q=0 maka Qnot=1 atau sebaliknya jika Q=1 maka Q not =0.

CRS Flip-Flop

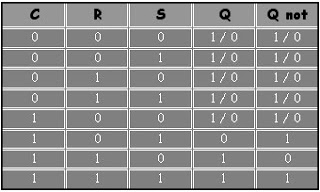

Tabel kebenarannya:

Keterangan:

1 / 0 = memory

Q = 0 [reset]

Q = 1 [set]

CRS Flip-flop adalah clocked RS-FF yang dilengkapi dengan sebuah terminal pulsa clock. Pulsa clock ini berfungsi mengatur keadaan Set dan Reset. Bila pulsa clock berlogik 0, maka perubahan logik pada input R dan S tidak akan mengakibatkan perubahan pada output Q dan Qnot. Akan tetapi apabila pulsa clock berlogik 1, maka perubahan pada input R dan S dapat mengakibatkan perubahan pada output Q dan Q not.

D Flip-Flop

D flip-flop adalah RS flip-flop yang ditambah dengan suatu inventer pada reset inputnya. Sifat dari D flip-flop adalah bila input D (Data) dan pulsa clock berlogik 1, maka output Q akan berlogik 1 dan bilamana input D berlogik 0, maka D flip-flop akan berada pada keadaan reset atau output Q berlogik 0.

Tabel Kebenaran:

T Flip-Flop

Tabel Kebenaran:

Rangkaian T flip-flop atau Togle flip-flop dapat dibentuk dari modifikasi clocked RSFF, DFF maupun JKFF. TFF mempunyai sebuah terminal input T dan dua buah terminal output Q dan Qnot. TFF banyak digunakan pada rangkaian Counter, frekuensi deviden dan sebagainya.

J-K Flip-Flop

JK flip-flop sering disebut dengan JK FF induk hamba atau Master Slave JK FF karena terdiri dari dua buah flip-flop, yaitu Master FF dan Slave FF. Master Slave JK FF ini memiliki 3 buah terminal input yaitu J, K dan Clock. Sedangkan IC yang dipakai untuk menyusun JK FF adalah tipe 7473 yang mempunyai 2 buah JK flip-flop dimana lay outnya dapat dilihat pada Vodemaccum IC (Data bookc IC). Kelebihan JK FF terhadap FF sebelumnya yaitu JK FF tidak mempunyai kondisi terlarang artinya berapapun input yang diberikan asal ada clock maka akan terjadi perubahan pada output.

Tabel Kebenaran :

1 komentar:

Terimakasih :-)

Posting Komentar